Blind Source/Signal Separation

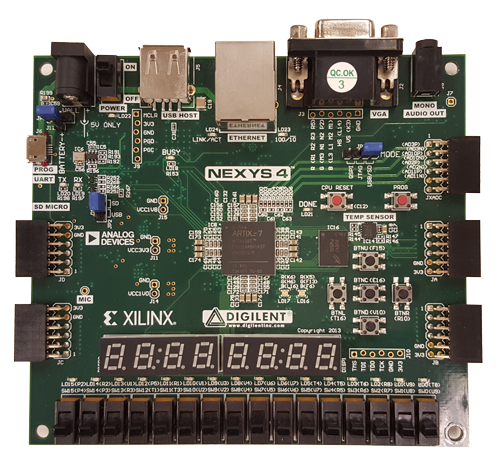

The current focus of our Blind Source Separation (BSS) topic is to implement a hardware version of several existing algorithms for performance comparison. Specifically, we are working towards an FPGA implementation. FPGA stands for Field Programmable Gate Array, and an FPGA implementation is one of the most optimal in terms of speed. Hardware implementation performance results will be presented in the thesis for this topic. Below is an example of an FPGA development board which we may use to implement the BSS algorithms of interest.

What is Blind Source Separation?

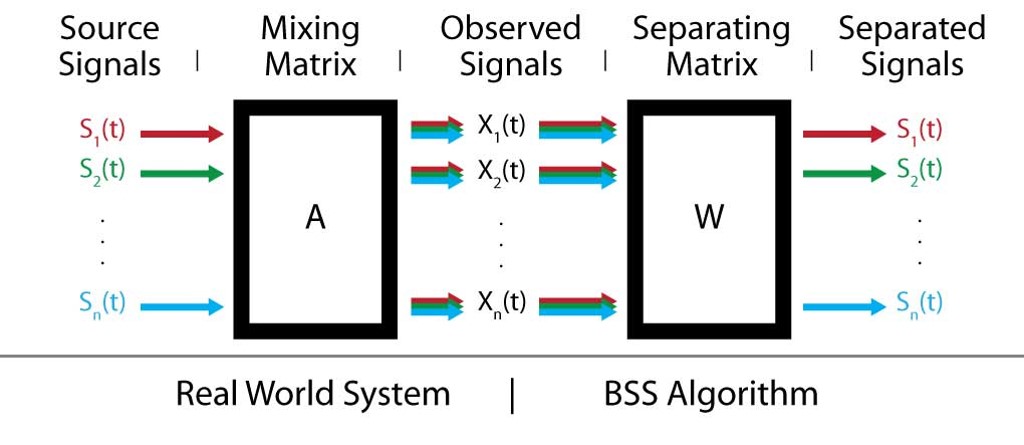

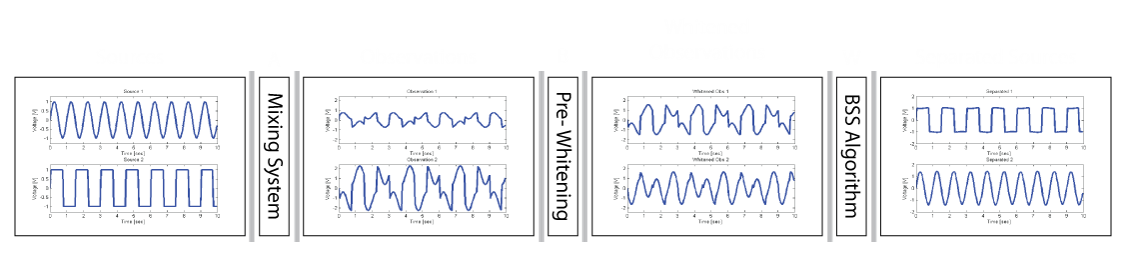

Blind Source Separation (BSS) is a technique for estimating a set of source signals without prior information about those signals, given a mixture of those signals.

BSS System Overview

Where can BSS be applied?

The idea of separating source signals given a mixture of signals is so general and broad that the applications of BSS algorithms are numerous.

Some examples:

- Separating Audio Signals (given a sample from a conversation, the goal is to extract clean samples of each individual speaking; one of the signals may be considered a noise source)

- Seismic Data Analysis (extract important signal trends in a noisy/mixed sample)

- Machine monitoring and error detection/analysis for things like assembly lines

- Medical (separate different signals from electronic signal monitoring)

- Data Mining (pick out trends in data)